Merge branch 'main' of https://git.beagleboard.org/docs/docs.beagleboard.io

Showing

- boards/beaglev/fire/02-quick-start.rst 4 additions, 1 deletionboards/beaglev/fire/02-quick-start.rst

- boards/beaglev/fire/05-demos.rst 3 additions, 1 deletionboards/beaglev/fire/05-demos.rst

- boards/beaglev/fire/demos-and-tutorials/flashing-board.rst 6 additions, 0 deletionsboards/beaglev/fire/demos-and-tutorials/flashing-board.rst

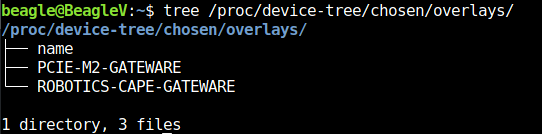

- boards/beaglev/fire/demos-and-tutorials/gateware/how-to-find-out-whats-on-the-board.rst 56 additions, 0 deletions...tutorials/gateware/how-to-find-out-whats-on-the-board.rst

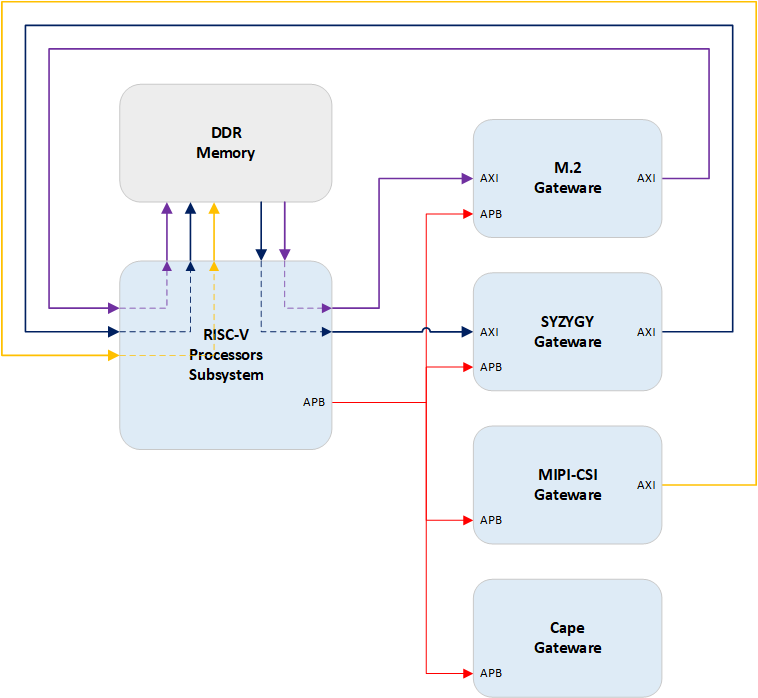

- boards/beaglev/fire/demos-and-tutorials/gateware/index.rst 82 additions, 0 deletionsboards/beaglev/fire/demos-and-tutorials/gateware/index.rst

- boards/beaglev/fire/demos-and-tutorials/gateware/media/Gateware-Flow-bitstream-builder-full-picture.png 0 additions, 0 deletions...re/media/Gateware-Flow-bitstream-builder-full-picture.png

- boards/beaglev/fire/demos-and-tutorials/gateware/media/Gateware-Flow-simplified-overview.png 0 additions, 0 deletions...ials/gateware/media/Gateware-Flow-simplified-overview.png

- boards/beaglev/fire/demos-and-tutorials/gateware/media/dts-design-info.png 0 additions, 0 deletions...re/demos-and-tutorials/gateware/media/dts-design-info.png

- boards/beaglev/fire/demos-and-tutorials/gateware/media/dts-design-version.png 0 additions, 0 deletions...demos-and-tutorials/gateware/media/dts-design-version.png

- boards/beaglev/fire/demos-and-tutorials/gateware/media/hss-design-info.png 0 additions, 0 deletions...re/demos-and-tutorials/gateware/media/hss-design-info.png

- boards/beaglev/fire/demos-and-tutorials/mchp-fpga-tools-installation-guide.rst 9 additions, 0 deletions...emos-and-tutorials/mchp-fpga-tools-installation-guide.rst

- boards/beaglev/fire/index.rst 15 additions, 11 deletionsboards/beaglev/fire/index.rst

56 KiB

22.9 KiB

16.3 KiB

12.6 KiB

10.5 KiB